GCC Build Process

*Build : 소스코드에서 실행 가능한 SW로 변환하는 과정(Process) 또는 결과물

.c 파일이 실행파일이 되는 과정이 빌드라고 한다면

전처리기 : .c -> .i 로 바뀌는 과정을 담당

컴파일러 : .i -> .s로 바뀌는 과정을 담당

어셈블러 : .s 파일을 -> .o 로 바꾸는 과정을 담당

컴파일 과정을 거치면, .i / .o / .s 파일들이 생기는 데, 대부분의 컴파일러들은 해당 파일을 보여주진 않음

흔히 컴파일이라고 하면, .c 가 .elf / .exe 가 되는 것으로 이해

컴파일러 라는 장치가 하는 역할을 컴파일이라고 축소해서 말하기도 하고, 컴파일이라는 큰 개념으로도 말하기도 한다.

C++ 언어 빌드 과정 : 다음 글 참고

https://lg960214.tistory.com/35

[C++] 프로그램 컴파일 과정 - 선행처리기(preprocessor), 컴파일러(compiler), 링커(linker)

C++ 프로그램 컴파일 과정 1. 소스 파일 작성 2. 선행처리기(preprocessor)에 의한 선행처리 3. 컴파일러(compiler)에 의한 컴파일 4. 링커(linker)에 의한 링크 1. 소스 파일 작성 소스 파일(.cpp) : C++ 문법에

lg960214.tistory.com

GCC는 실행 파일까지 한 번에 생성할 수 있지만, 과정을 보기 위해 Compile, link 과정을 나눠서 진행해본다.

GCC로 Complie & Assemble 진행하기

vi를 이용해서 다음 파일을 생성

# Compile & Assemble 진행

$ gcc -c ./green.c

$ gcc -c ./yellow.c

GCC로 Linking 진행하기

# linking 진행 - 오브젝트 파일이 여러 개면, 병렬로 계속 작성하면 됨

$ gcc ./[오브젝트 파일 1] ./[오브젝트 파일 2] ... -o [실행 파일 이름]

빌드 자동화 스크립트

Build System

Build 시 필요한 여러 작업을 도와주는 프로그램을 의미, 대표적으로 make, cmake가 있다.

make란?

Makefile이라는 텍스트 파일에 작성된 빌드 규칙에 따라 소프트웨어를 빌드하는 도구

장점

- Build 자동화 : 기술된 순서대로 Build 작업을 수행하는 자동화 스크립트 지원

- Build 속도 최적화 : 불필요한 Compile & Assemble 피하기

make 설치

$ sudo apt install make -y

make 사용하기

먼저, vi를 이용해 다음과 같이 파일 생성

vi를 이용해 Makefile 이라는 스크립트 파일 생성

이후 스크립트 실행해본다.

$ make

기존 build.sh를 이용한 방식은 .c 파일이 하나라도 수정될 시 모든 .o 파일이 재생성 후 build 되는데

make를 이용하면 필요한 부분만 update 후 파일을 실행파일을 생성한다. (최적화)

cmake란?

CMakeLists.txt(철자 주의!!)라는 텍스트 파일에 작성된 빌드 규칙에 따라 소프트웨어를 빌드하는 도구

make 같이 build를 직접적으로 하는 도구가 아니라, Makefile을 자동 생성할 수 있는 Build System

cmake 설치

$ sudo apt install g++ cmake –y

cmake 사용하기

먼저, CMakeLists.txt 파일을 작성한다.

# CmakeLists.txt 파일 내용

# 가장 처음 들어가는 인자인 gogo는 최종적으로 만들어질 실행파일 이름을 의미

ADD_EXECUTABLE(gogo main.c blue.c pink.c)

다음 cmake 명령어 수행하면 된다.

$ cmake .

이후 위에서 언급한 make 방식으로 스크립트를 실행하고, 실행 파일을 테스트해보면 된다.

make 스크립트 활용하기

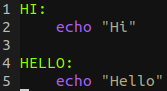

새로운 디렉토리에서, Makefile 새로 작성

Makefile 실행

# 그냥 make 실행 시, 첫 번 째 명령어 실행

$ make

# echo "Hi"

# Hi

$ make HI

# echo "Hi"

# Hi

$ make HELLO

# echo "Hello"

# Hello

Makefile에서, echo 앞에 @를 붙이면, 수행할 명령어가 생략하고 결과만 출력한다.

# Shell Script 명령어 @ 삽입 시

$ make

# Hi

$ make HI

# Hi

$ make HELLO

# Hello

의존성 타겟 (Dependency Target)

다음과 같이 코드 작성 후, 결과 실행해보면 의존성 타겟이 무엇인 지 알 수 있다.

매크로 추가

Make에서는 변수가 아니라 "매크로" 라고 부른다.

0. 보통 매크로는 가장 위에 정의한다.

1. MSG1, MSG2 등 매크로는 아무 곳에나 넣어도 동작한다. (일종의 hoisting 개념)

2. 정의되지 않은 매크로는 빈 칸으로 출력된다.

- 1st line : asdasd는 정의되지 않았기 때문에 빈 칸으로 출력

- 2nd line : MSG1의 내용이 echo됨

- 3rd line : MSG2의 내용이 echo됨

- 4th line : "Hi" 가 echo됨

*echo 명령어 특징

# 1. echo 명령어는 띄어쓰기를 1개만 허용한다

# Makefile 작성 시에도 똑같이 적용됨

$ echo "Hi" "ABC"

# Hi ABC

$ echo "Hi" "ABC"

# Hi ABC

# 2. echo 명령어는 문자 그대로 출력됨 (계산되지 않음)

$ echo 13 + 55

# 13 + 55

$ echo "BTS" ABC BB

# BTS ABC BB

$ echo 'ABC' bbq

# ABC bbq

3. 매크로에 더하기 연산자(+) 사용 시, 공백이 추가로 입력됨

4. 대입 연산자에는 Simple Equal(:=) 과 Reculsive Equl(=) 두 가지가 있다.

- ' := ' : "Script 순서"대로 현재 기준에서 값을 넣는다 / 3번째 줄까지 NAME은 "OH" 이므로, OH를 출력

- ' = ' : (모든 매크로 계산이 끝난) 최종 변수 결과를 집어 넣는다.

5. $@ : Target을 나타내는 변수

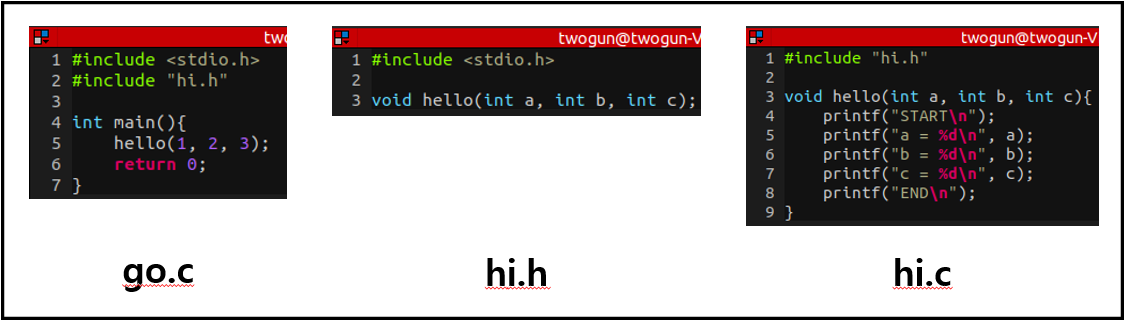

GCC MakeFile

1. 다음과 같이 소스코드 파일을 준비

2. Makefile 소스 코드 작성

3. make 명령어로 실행

4. 컴파일러를 변수로 변경하기

*임베디드 환경에서, 컴파일러가 바뀔 수 있기 때문에 다음을 매크로를 이용해 진행해본다.

- CC 매크로를 이용해 컴파일러 명령어(gcc) 선정

- $@ 을 이용해 의존성 타겟을 선정

- $^ : 의존성 파일을 나타냄

- $< : 의존성 파일 중 첫 번째 파일을 나타냄

2번에서 작성한 코드와 동일하게 작동함